5G meets AI

World’s first Base Station-on-a-Chip.

Scalable Silicon

From small cell to macro-cells

5G & AI

Natively integrated

Production Ready

4G/5G physical layer

RISC-V Architecture

Rich, open software ecosystem

We make

small cells easy

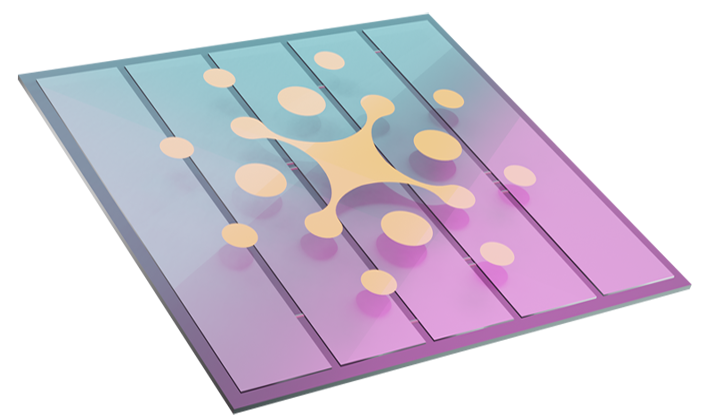

Entire Base Station-on-a-Chip for Small Cells

Production Grade 4G/5G

Fully Integrated Baseband + NPU + CPU + Timing + FEC

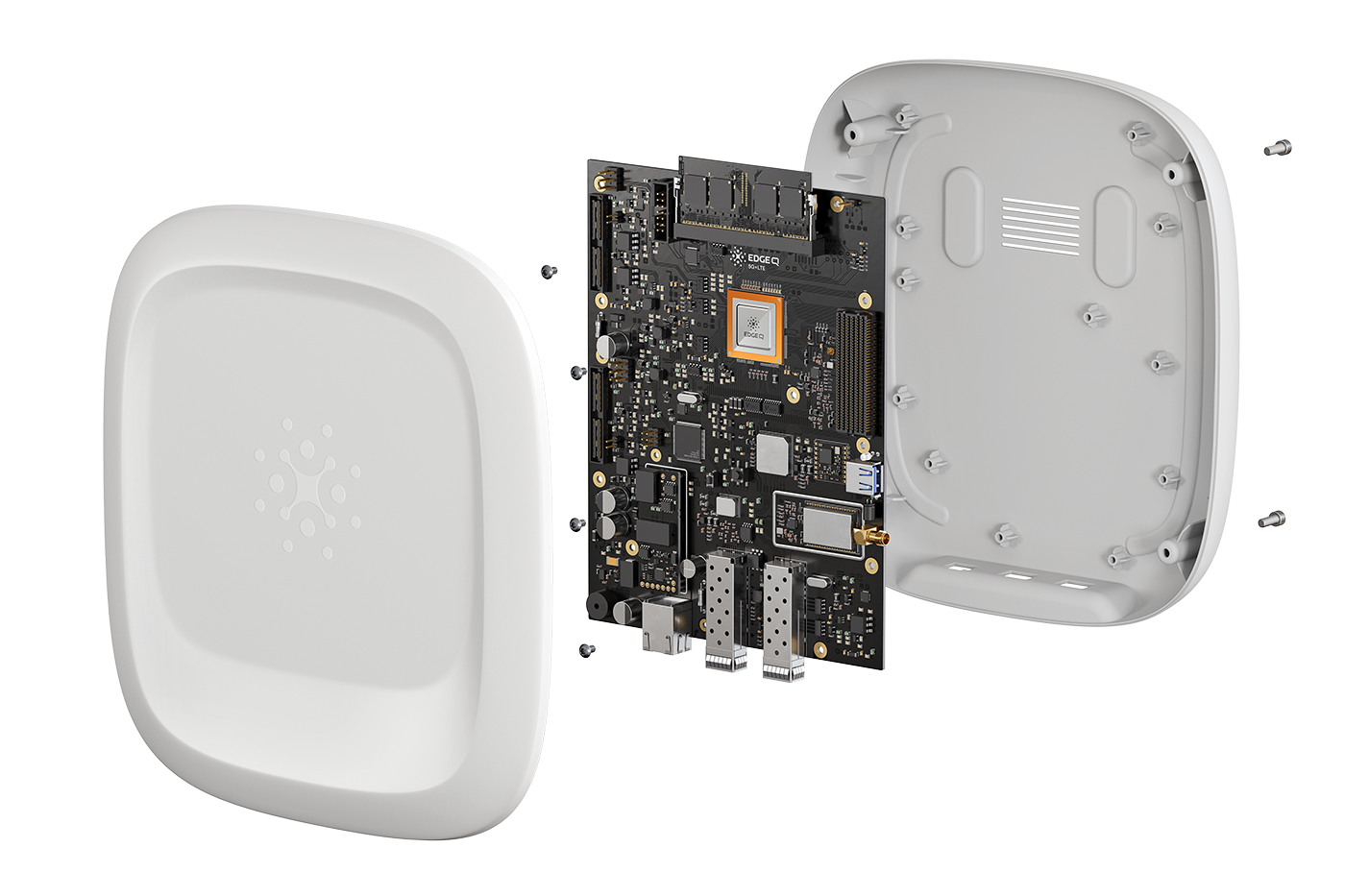

Product OverviewAll-in-One

Small Cell with Option 0,2

5G + LTE

Single SoC for LTE & 5G

Power Over Ethernet Envelope

Ultra-Low Power

Software Upgradeable

Field Upgradeable 3GPP Standards

And big cells

even easier

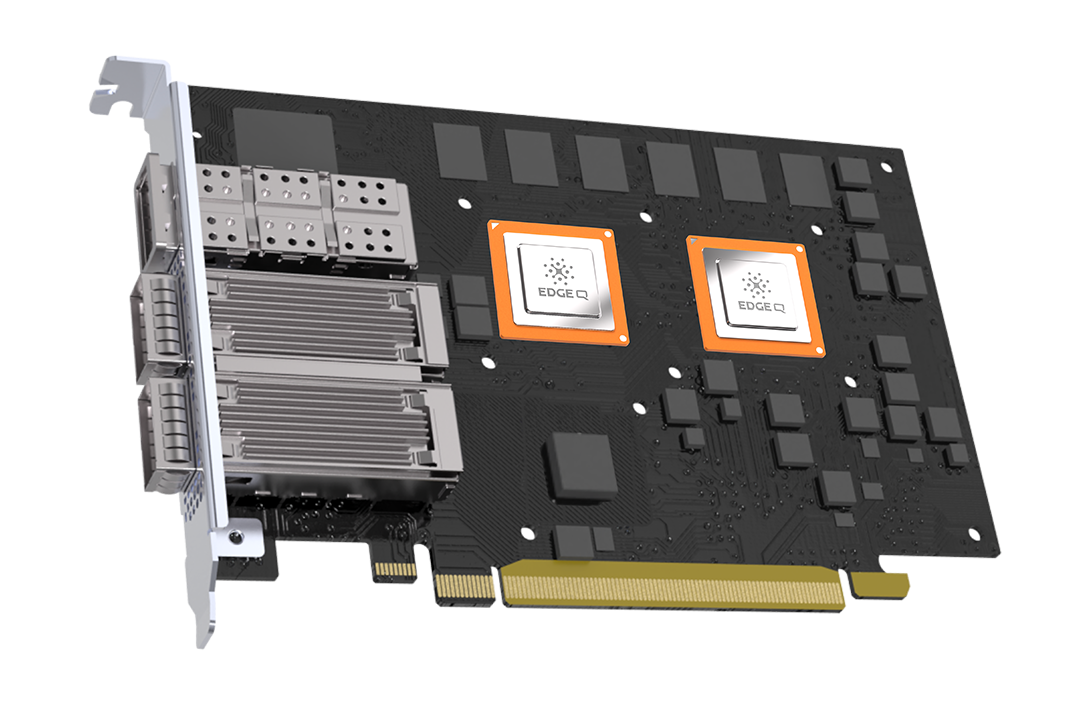

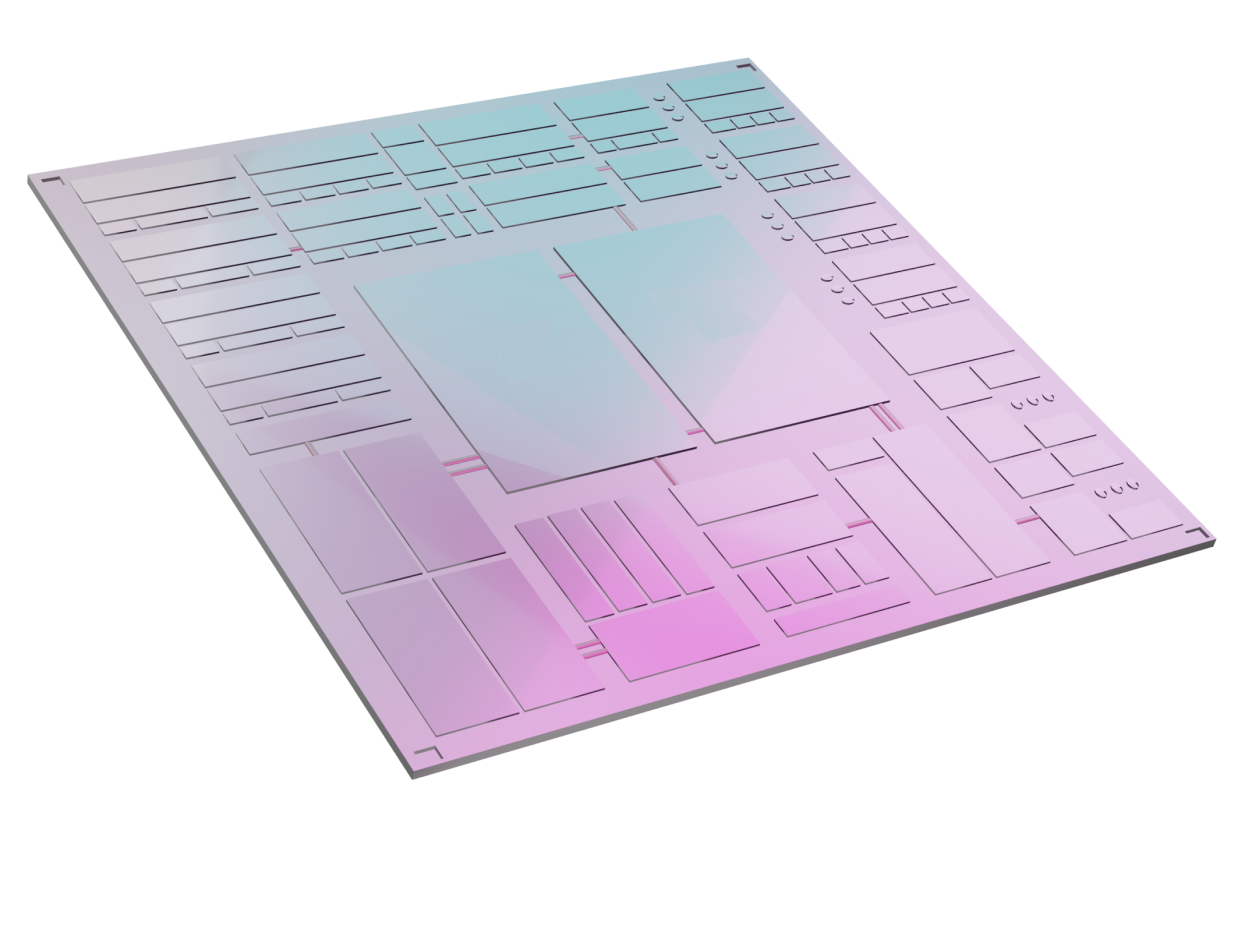

Fully In-Line L1 Acceleration PCIe Card

5:1 Multiple Base station Components Integrated into 1 Chip

1/5 the Power of Current Solutions

Natively Scales Across Cell Sites to Pre-aggregation Data Center

Product OverviewAll-in-One

Integrated Timing Sync

ORAN Compliant

Supports all ORAN splits 6/7.x

Multi-RAT (4G + 5G) Support

Same chip. Same software.

Massive MIMO Compliant

Scales up to 64 TRX

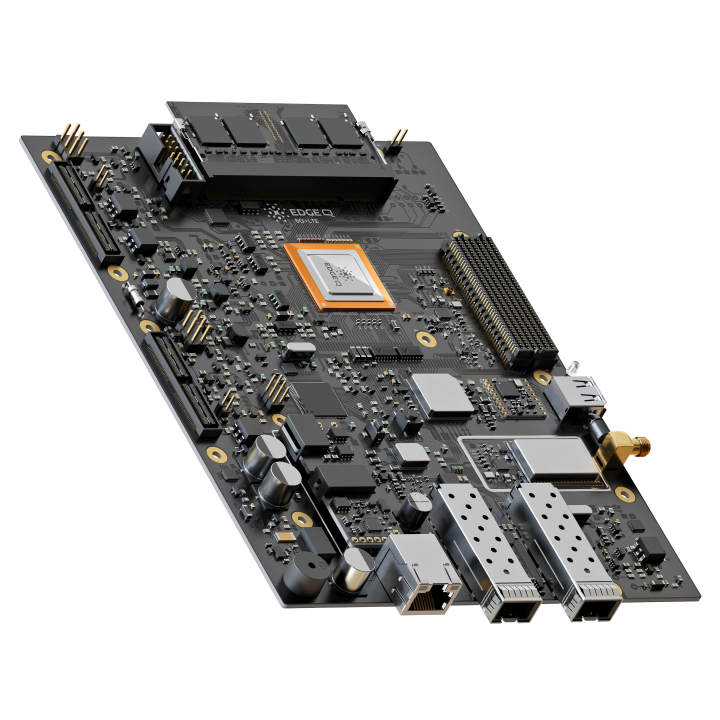

Reference board,

for builders

EdgeQ’s own 4G + 5G reference design used for small cell and open RAN development.

Target Use: eNB, gNB SA, gNB NSA, ORAN DU development

Contact UsAll-In-One Hardware

Baseband + NPU + CPU + RFIC & RFEE (from partners)

Multi-Mode 4G + 5G

Carrier-Ready PHY + L2/L3 Stack

Software Development Kit

Latest Linux Kernel, FAPI APIs, GNU Development Tool Chain, etc...

Hover over our silicon to learn more.

Hover over our silicon to learn more.

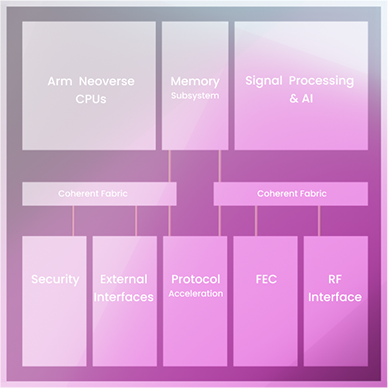

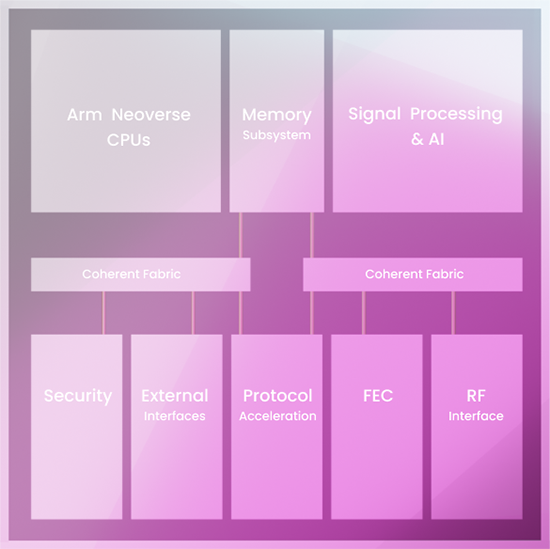

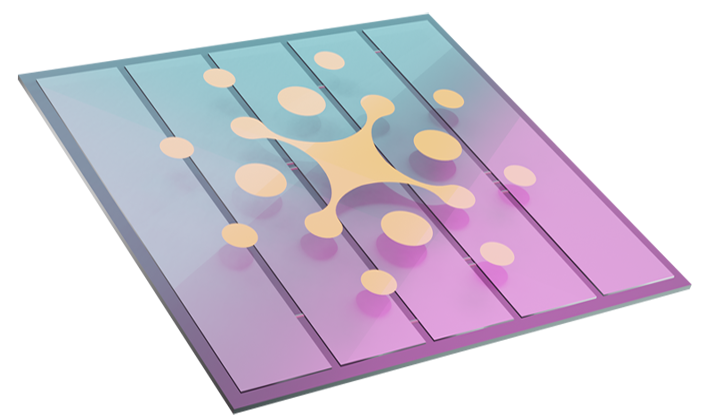

The bas(IC)s of our base station

Massive integration of 5G + AI + NPU +CPU

It’s all based on our software-defined 5G radio giving you

RU, DU, and gNB capabilities.

Software-defined PHYsical layer

Deployable, carrier-grade 4G/5G PHY built by us

with customizable L1 functions:

- Waveform processing

- Accelerated FEC

- Beamforming

- Constellation mapping

- Channel Estimation & Equalization

- Complex Integer Ops

- Scrambling \ Descrambling

- Layer Mapping and more...

We run it all

L2/L3

Our SoC is a one-stop-shop with L2/L3

functionalities running on our host CPU:

- Scheduler

- nFAPI interface

- Power control

- Mobility

- MAC, RLC, PDCP Processing

and more...